VHDL IMPLEMENTATION OF REED-SOLOMON CODING

₹1500-12500 INR

Cerrado

Publicado hace casi 8 años

₹1500-12500 INR

Pagado a la entrega

VHDL IMPLEMENTATION OF

REED-SOLOMON CODING

Forward Error Correction technique depending on the properties of the system or on the application in which the error correcting is to be introduced. Error control coding techniques are based on the addition of redundancy to the information message according to a prescribed rule thereby providing data a higher bit rate. This redundancy is exploited by decoder at the receiver end to decide which message bit actually transmitted. Reed-Solomon codes are an important sub – class of non binary Bose-Chaudhuri-Hocquenghem (BCH) codes.

In digital communication, Reed-Solomon (RS) codes refer to as a part of channel coding that had becoming very significant to better withstand the effects of various channel impairments such as noise, interference and fading. This signal processing technique is designed to improve communication performance and can be deliberate as medium for accomplishing desirable system trade-offs.

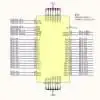

Galois field arithmetic is used for encoding and decoding of Reed – Solomon codes. Galois field multipliers are used for encoding the information block. The encoder attaches parity symbols to the data using a predetermined algorithm before transmission. At the decoder, the syndrome of the received codeword is calculated. VHDL implementation creates a flexible, fast method and high degree of parallelism for implementing the Reed – Solomon codes.

The purpose of this thesis is to evaluate the performance of RS coding system using M-ary modulation over Additive White Gaussian Noise AWGN channel and implementation of RS encoder in VHDL. Computer simulation tool and MATLAB will be used to create and run extensively the entire simulation model for performance evaluation and VHDL is used to implemented the design of RS encoder.

ID del proyecto: 10408647

Información sobre el proyecto

6 propuestas

Proyecto remoto

Activo hace 8 años

¿Buscas ganar dinero?

Beneficios de presentar ofertas en Freelancer

Fija tu plazo y presupuesto

Cobra por tu trabajo

Describe tu propuesta

Es gratis registrarse y presentar ofertas en los trabajos

Sobre este cliente

NANDED, India

1

Forma de pago verificada

Miembro desde jul 22, 2015

Verificación del cliente

Otros trabajos de este cliente

₹1500-12500 INR

₹1500-12500 INR

₹600-1500 INR

₹1500-12500 INR

₹1500-12500 INR

Trabajos similares

min €36 EUR / hour

$10-100 USD

$10-65 USD

$10-60 USD

₹75000-150000 INR

$10-50 AUD

$250-750 USD

$1500-3000 USD

₹37500-75000 INR

$25-50 USD / hour

₹600-1500 INR

$3-10 SGD / hour

$30-250 USD

¡Gracias! Te hemos enviado un enlace para reclamar tu crédito gratuito.

Algo salió mal al enviar tu correo electrónico. Por favor, intenta de nuevo.

Cargando visualización previa

Permiso concedido para Geolocalización.

Tu sesión de acceso ha expirado y has sido desconectado. Por favor, inica sesión nuevamente.